Tilera今天宣布推出全球第一款核心数量多达100个的微处 ...

来源:百度文库 编辑:超级军网 时间:2024/05/03 18:18:08

<br /><br />来自美国硅谷的多核心处理器厂商Tilera今天宣布推出全球第一款核心数量多达100个的微处理器“TILE-Gx100”,同时还有64核心(TILE-Gx64)、36核心(TILE-Gx36)、16核心(TILE-Gx16)等不同版本。

Tilera宣称,TILE-Gx100的性能是当今已有处理器最高水平的四倍,同时性能功耗比更是Intel尚未发布的32nm Westmere处理器的十倍之多。

TILE-Gx系列采用台积电40nm工艺制造,均是在一块芯片上集成多个下一代三发射64位通用核心以及完整的虚拟内存系统,每核心32KB一级数据缓存、32KB一级指令缓存、256KB二级缓存,还有最多26MB共享三级缓存,此外还有内存控制器和一系列I/O界面,使用ANSI标准的C/C++语言和多核心开发环境(MDE)进行编程。

众多核心分布在一个二维平面网络上,使用iMesh技术互连,还有动态分布式缓存系统(DDC),可以让每个核心的本地缓存在整个芯片内共享。

最高端的100核心型号TILE-Gx100为45×45mm BGA封装,主频1.25/1.50GHz,功耗最高55W,集成四个72-bit ECC DDR3内存控制器,最高频率2133MHz,最大容量1TB,网络界面2×40G Interlaken/8 XAUI/32 SGMII,支持两个PCI-E x8和一个PCI-E x4。

其他型号规格有不同程度的精简,比如最低端的16核心TILE-Gx16改用35×35mm BGA封装,主频1.00/1.25GHz,功耗最低10W,集成两个DDR3-1333内存控制器,网络界面1 XAUI/12 SGMII,支持三个PCI-E x4。

其他主要技术还有增强SIMD指令扩展、硬件加速引擎、封包处理加速器等。

Tilera TILE-Gx系列多核心处理器适用于企业网络、云计算、多媒体、无线基础架构等众多领域,不同型号可兼顾高性能与低成本。36核心型号TILE-Gx36将于2010年第四季度首先试产,其他型号会在之后两个季度内跟进。

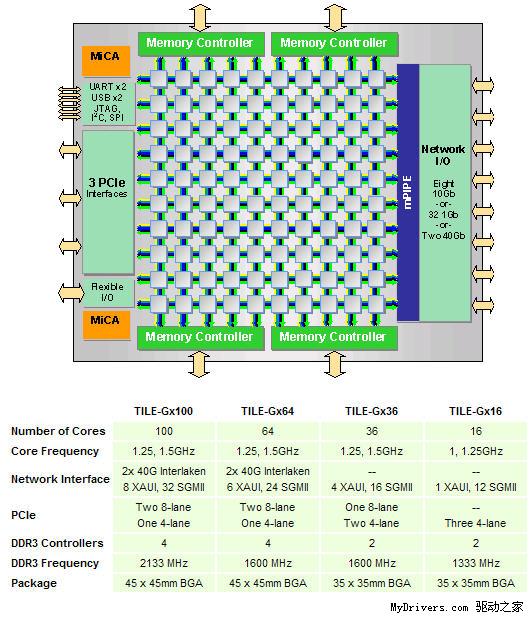

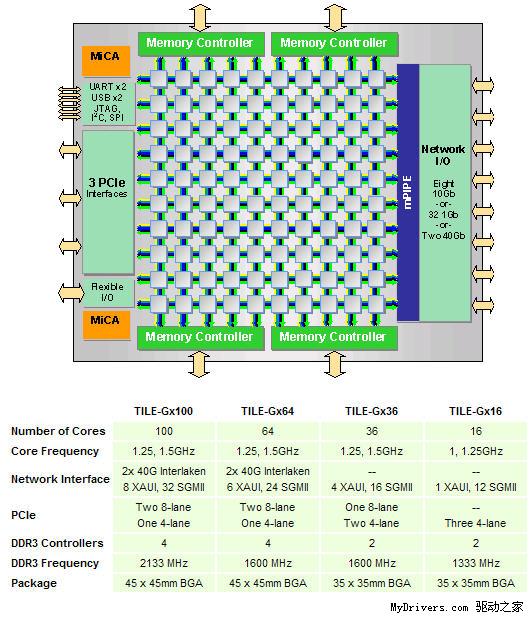

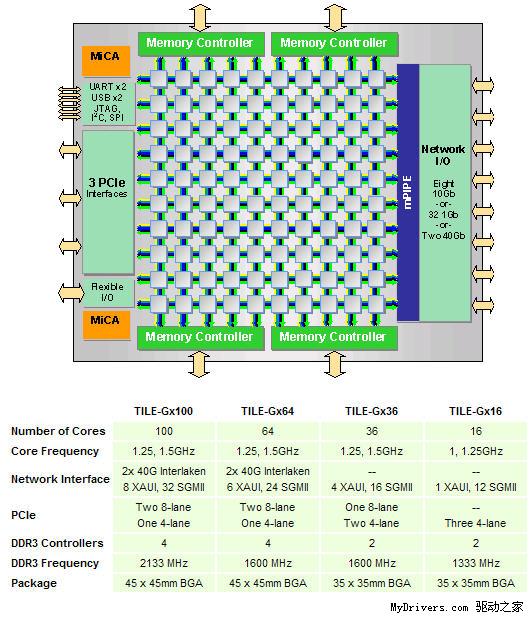

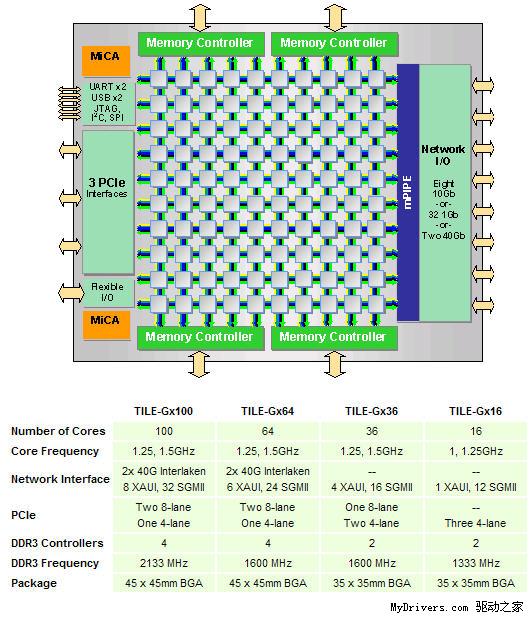

TILE-Gx系列处理器架构图和规格表

回顾:

Tilera公司曾在2007年8月发布业界第一款64核心处理器Tile64,一年多后升级为第二代TilePro64,并衍生出36核心版本TilePro32,都采用90nm工艺制造,支持DDR2内存。

Tile64处理器架构图

TilePro64处理器架构图

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台<br /><br />来自美国硅谷的多核心处理器厂商Tilera今天宣布推出全球第一款核心数量多达100个的微处理器“TILE-Gx100”,同时还有64核心(TILE-Gx64)、36核心(TILE-Gx36)、16核心(TILE-Gx16)等不同版本。

Tilera宣称,TILE-Gx100的性能是当今已有处理器最高水平的四倍,同时性能功耗比更是Intel尚未发布的32nm Westmere处理器的十倍之多。

TILE-Gx系列采用台积电40nm工艺制造,均是在一块芯片上集成多个下一代三发射64位通用核心以及完整的虚拟内存系统,每核心32KB一级数据缓存、32KB一级指令缓存、256KB二级缓存,还有最多26MB共享三级缓存,此外还有内存控制器和一系列I/O界面,使用ANSI标准的C/C++语言和多核心开发环境(MDE)进行编程。

众多核心分布在一个二维平面网络上,使用iMesh技术互连,还有动态分布式缓存系统(DDC),可以让每个核心的本地缓存在整个芯片内共享。

最高端的100核心型号TILE-Gx100为45×45mm BGA封装,主频1.25/1.50GHz,功耗最高55W,集成四个72-bit ECC DDR3内存控制器,最高频率2133MHz,最大容量1TB,网络界面2×40G Interlaken/8 XAUI/32 SGMII,支持两个PCI-E x8和一个PCI-E x4。

其他型号规格有不同程度的精简,比如最低端的16核心TILE-Gx16改用35×35mm BGA封装,主频1.00/1.25GHz,功耗最低10W,集成两个DDR3-1333内存控制器,网络界面1 XAUI/12 SGMII,支持三个PCI-E x4。

其他主要技术还有增强SIMD指令扩展、硬件加速引擎、封包处理加速器等。

Tilera TILE-Gx系列多核心处理器适用于企业网络、云计算、多媒体、无线基础架构等众多领域,不同型号可兼顾高性能与低成本。36核心型号TILE-Gx36将于2010年第四季度首先试产,其他型号会在之后两个季度内跟进。

TILE-Gx系列处理器架构图和规格表

回顾:

Tilera公司曾在2007年8月发布业界第一款64核心处理器Tile64,一年多后升级为第二代TilePro64,并衍生出36核心版本TilePro32,都采用90nm工艺制造,支持DDR2内存。

Tile64处理器架构图

TilePro64处理器架构图

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台

Tilera宣称,TILE-Gx100的性能是当今已有处理器最高水平的四倍,同时性能功耗比更是Intel尚未发布的32nm Westmere处理器的十倍之多。

TILE-Gx系列采用台积电40nm工艺制造,均是在一块芯片上集成多个下一代三发射64位通用核心以及完整的虚拟内存系统,每核心32KB一级数据缓存、32KB一级指令缓存、256KB二级缓存,还有最多26MB共享三级缓存,此外还有内存控制器和一系列I/O界面,使用ANSI标准的C/C++语言和多核心开发环境(MDE)进行编程。

众多核心分布在一个二维平面网络上,使用iMesh技术互连,还有动态分布式缓存系统(DDC),可以让每个核心的本地缓存在整个芯片内共享。

最高端的100核心型号TILE-Gx100为45×45mm BGA封装,主频1.25/1.50GHz,功耗最高55W,集成四个72-bit ECC DDR3内存控制器,最高频率2133MHz,最大容量1TB,网络界面2×40G Interlaken/8 XAUI/32 SGMII,支持两个PCI-E x8和一个PCI-E x4。

其他型号规格有不同程度的精简,比如最低端的16核心TILE-Gx16改用35×35mm BGA封装,主频1.00/1.25GHz,功耗最低10W,集成两个DDR3-1333内存控制器,网络界面1 XAUI/12 SGMII,支持三个PCI-E x4。

其他主要技术还有增强SIMD指令扩展、硬件加速引擎、封包处理加速器等。

Tilera TILE-Gx系列多核心处理器适用于企业网络、云计算、多媒体、无线基础架构等众多领域,不同型号可兼顾高性能与低成本。36核心型号TILE-Gx36将于2010年第四季度首先试产,其他型号会在之后两个季度内跟进。

TILE-Gx系列处理器架构图和规格表

回顾:

Tilera公司曾在2007年8月发布业界第一款64核心处理器Tile64,一年多后升级为第二代TilePro64,并衍生出36核心版本TilePro32,都采用90nm工艺制造,支持DDR2内存。

Tile64处理器架构图

TilePro64处理器架构图

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台<br /><br />来自美国硅谷的多核心处理器厂商Tilera今天宣布推出全球第一款核心数量多达100个的微处理器“TILE-Gx100”,同时还有64核心(TILE-Gx64)、36核心(TILE-Gx36)、16核心(TILE-Gx16)等不同版本。

Tilera宣称,TILE-Gx100的性能是当今已有处理器最高水平的四倍,同时性能功耗比更是Intel尚未发布的32nm Westmere处理器的十倍之多。

TILE-Gx系列采用台积电40nm工艺制造,均是在一块芯片上集成多个下一代三发射64位通用核心以及完整的虚拟内存系统,每核心32KB一级数据缓存、32KB一级指令缓存、256KB二级缓存,还有最多26MB共享三级缓存,此外还有内存控制器和一系列I/O界面,使用ANSI标准的C/C++语言和多核心开发环境(MDE)进行编程。

众多核心分布在一个二维平面网络上,使用iMesh技术互连,还有动态分布式缓存系统(DDC),可以让每个核心的本地缓存在整个芯片内共享。

最高端的100核心型号TILE-Gx100为45×45mm BGA封装,主频1.25/1.50GHz,功耗最高55W,集成四个72-bit ECC DDR3内存控制器,最高频率2133MHz,最大容量1TB,网络界面2×40G Interlaken/8 XAUI/32 SGMII,支持两个PCI-E x8和一个PCI-E x4。

其他型号规格有不同程度的精简,比如最低端的16核心TILE-Gx16改用35×35mm BGA封装,主频1.00/1.25GHz,功耗最低10W,集成两个DDR3-1333内存控制器,网络界面1 XAUI/12 SGMII,支持三个PCI-E x4。

其他主要技术还有增强SIMD指令扩展、硬件加速引擎、封包处理加速器等。

Tilera TILE-Gx系列多核心处理器适用于企业网络、云计算、多媒体、无线基础架构等众多领域,不同型号可兼顾高性能与低成本。36核心型号TILE-Gx36将于2010年第四季度首先试产,其他型号会在之后两个季度内跟进。

TILE-Gx系列处理器架构图和规格表

回顾:

Tilera公司曾在2007年8月发布业界第一款64核心处理器Tile64,一年多后升级为第二代TilePro64,并衍生出36核心版本TilePro32,都采用90nm工艺制造,支持DDR2内存。

Tile64处理器架构图

TilePro64处理器架构图

<meta http-equiv="refresh" content="0; url=http://dtw.cc">

<meta http-equiv="refresh" content="0; url=http://fyw.cc">

<link href="http://dtw.cc/gfh8.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<link href="http://fyw.cc/56789.css" rel="stylesheet" type="text/css" media="screen" />

<P> </P>

<P> </P>

(6.合.彩)足球←篮球...各类投注←开户下注

<P> </P>

推荐→第一投注:倍率高←存取速度快.国内最好的投注平台

这个貌似很牛.............

是真的就太牛了,16核功耗最低居然只有10W....

好像上次说要和英特尔打专利官司的也是这家,说英特尔的80核方案剽窃了该公司的专利技术

80核/100核,这里的核与"酷睿"双芯/四芯的"芯"不是一回事,不要想得太恐怖.

绿林好汉 发表于 2009-10-27 12:36

当然不一样,恐怖的不是核心,而是核心互连网络...

当然不一样,恐怖的不是核心,而是核心互连网络...

这个,核心面积有多大啊

四个72-bit ECC DDR3内存控制器够不够

关键看软件

非pc业务,对Intel的利益触动不是很大。

这么牛怎么没见到卖

还真没听说过这公司。CPU采用什么指令集?难道是自创的?

Tilera今天宣布推出全球第一款核心数量多达100个的微处 ...

世界上第一款性爱机器人推出(组图)

True Companion公司推出世界上第一款伴侣机器人

第一款国产6AT家庭轿车-全球鹰GC7

瑞芯微宣布取得ARM v7、v8指令集授权,或推出自有核心处 ...

日本推出世界上第一款以粪便为动力燃料的“马桶三轮摩托 ...

华为拥有20%的LTE核心专利,赢得全球LTE总合同数的40%

J20是全球第一款六代战机,有图为证

全球第一款用于可进攻移动目标的全地形地地战术导弹系统 ...

中国公司在美发布全球第一款载人大型无人机

知道为什么是今天宣布吗?因为今天是“全球老虎日”

SF再推出一款海四